- May 7, 2006 at 9:14pm

Initial revision of source distribution on CVS at OpenCircuitDesign (Revision 86).

Also: Corrections to the handling of output scale for PostScript output (was divided by 2), and added handling of output offset in the Print dialog. Corrected errors in the Tcl "print" command for offset and scale. Note that this is a global offset, and applies to all output devices. There ought to be an equivalent handling of device margins (part of the device structure).- May 26, 2006 at 2:40am

2006-05-25 16:13 tim A number of changes: 1) Added "clearance" and "selected_clearance" command options for "line" and "via" commands, and a "clearance" option for the "pin" command. 2) Changed clearance setting behavior so that a clearance of zero can be specified (clearances between zero and the minimum DRC spacing rule are not allowed) 3) Changed the DRC rules so that a clearance of zero is not reported as a DRC violation. 4) Reduced many of the "minimum" contants to reflect the capabilities of advanced printed circuit board manufacturing.- June 14, 2006 at 2:40am

2006-06-14 01:04 eric Cleaned up build files Removed un-needed Makefiles Added test RPM spec file

Also: Removed files which are generated

Also: Removed building of pad.* files in doc folder as they seem to no longer exist

Also: Updated RPM spec file First attempt at fixing rpath problem on x86_64- June 15, 2006 at 2:40am

Removed files which are generated

Also: Removed building of pad.* files in doc folder as they seem to no longer exist

Also: Updated RPM spec file First attempt at fixing rpath problem on x86_64

Also: 2006-06-14 11:36 tim Removed all references to the unused program "tgif".- June 16, 2006 at 2:40am

2006-06-15 11:38 tim Changed "SCROLL_TIME" to a sane value.- June 20, 2006 at 2:40am

2006-06-19 13:10 tim Corrected the connectivity-finding routine to connect vias with zero clearance to surrounding polygons.- June 21, 2006 at 2:40am

2006-06-20 09:41 tim Added the capability to handle plugged vias. There is no output format for plugged vias (yet), but the display works and DRC handles them correctly.

Also: Added output drill file for plugged vias.- October 24, 2006 at 2:40am

2006-10-23 11:11 tim Some changes to attempt to make the Tcl/Tk libraries work correctly, esp. for Solaris as reported by Hans Albertsson.- November 5, 2006 at 2:40am

2006-11-04 08:06 tim Changed the parser so that it accepts (although does not handle) the 6-entry DRC line from pcb20060822.- November 6, 2006 at 2:40am

Implemented minimum drill width to match the syntax used by pcb20060822 (I have decided *not* to implement minimum annular ring until I determine that any vendor has a different rule above and beyond minimum route width).- February 17, 2012 at 3:00am

Corrections to the compilation, similar to changes made long ago for other programs, making tkcon.tcl compatible with different versions of wish (e.g., wish8.5), and able to find and use the version that the tool was compiled to.

Also: Update at Thu Feb 16 11:54:06 PST 2012 by tim

Also: Merge branch 'master' into work

- August 16, 2013 at 3:00am

Minor---cleanup of some compile-time files that got checked in with the rest.

- October 1, 2013 at 3:00am

Removed a bunch of files by doing "make distclean"

- March 26, 2019 at 3:00am

Made trivial change to test the git repo implementation.

- May 7, 2019 at 3:00am

Removed VERSION from .gitignore (the right way, in master branch).

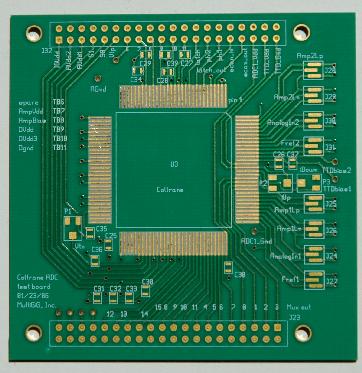

![]()

For questions regarding the Tcl/Tk-based branch of PCB, please contact:

tim@opencircuitdesign.com

For questions regarding the original PCB code, please contact:

harry.eaton@jhuapl.edu

Last updated: May 7, 2019 at 9:11am