# TimberWolf-6.1

### Mixed Macro / Standard Cell Floorplanning, Placement and Routing Package

(Building Block, Gate Array, and Standard Cell Circuits)

Yale University

May 1, 1992

## Table of Contents

| 1.        | Introduction                                         | .2    |

|-----------|------------------------------------------------------|-------|

| 2.        | Features                                             |       |

| 3.        | Using This Manual                                    | .3    |

| 4.        | Compilation of TimberWolf                            | .4    |

| 5.        | TimberWolf Input Files                               | .6    |

|           | 5.1. The Format of the CircuitName.par File          | .6    |

|           | 5.1.1. Genrows parameters.                           |       |

|           | 5.1.2. MINC - Mincut parameters                      | .9    |

|           | 5.1.3. MICK - Mickey parameters                      | .9    |

|           | 5.1.4. PART - Tomus parameters                       |       |

|           | 5.1.5. SGGR - Sea-of-gates global router parameters  |       |

|           | 5.1.6. TWMC - TimberWolfMC parameters                |       |

|           | 5.1.7. TWSC - TimberWolfSC parameters                | .14   |

|           | 5.2. The Format of the circuitName.cel File          |       |

|           | 5.2.1. Standard Cell / Gate Array Cell Definition    |       |

|           | 5.2.2. Hard Macro Cell Definition                    |       |

|           | 5.2.3. Soft Macro Cell Format                        |       |

|           | 5.2.4. Pad Description Format                        |       |

|           | 5.3. The Format of the CircuitName.net File          |       |

| 6.        | TimberWolf Output Files                              |       |

| 0.        | 6.1. Message Files                                   |       |

|           | 6.2. Placement Output Files                          |       |

|           | 6.3. Global Routing Output Files                     | 44    |

| 7.        | Executing TimberWolf                                 |       |

| 7.<br>8.  | Tutorial #1 - Macro Cell Design                      |       |

| 0.<br>9.  | Tutorial #2 - Standard Cell Design                   |       |

| ).<br>10. | Tutorial #3 - Mixed Macro/Standard Cell Design       |       |

| 11.       | Tutorial #4 - N-way Circuit Partitioning using Tomus |       |

| 12.       | Genrows - Row Generation Program.                    |       |

| 12.       | 12.1. Function                                       |       |

|           |                                                      |       |

|           | 12.2. Input                                          |       |

|           | 12.3. Output                                         |       |

| 12        | 12.4. Graphical Interface                            |       |

| 13.       | Mickey                                               |       |

|           | 13.1. Function                                       |       |

|           | 13.2. Input                                          |       |

|           | 13.3. Output                                         | . / 3 |

| 1.4       | 13.2. Graphical Interface                            |       |

| 14.       | Mincut - Standard cell clustering                    |       |

|           | 14.1. Function                                       |       |

|           | 14.2. Input                                          |       |

|           | 14.3. Output                                         |       |

|           | 14.4. Graphical Interface                            |       |

| 15        | PSC                                                  |       |

|           | 15.1. Function                                       |       |

|           | 15.2. Input                                          |       |

|           | 15.3. Output                                         |       |

|           | 15.4. Graphical Interface                            | .78   |

| 16.       | SGGR                                                 |       |

|           | 16.1. Function                                       | .80   |

|           | 16.2. Input                                          | .80   |

|           | 16.3. Output                                         | .80   |

|           | 16.4. Graphical Interface                            | .80   |

| 17.       | Syntax                                               | .81   |

|           | 17.1. Function                                       | .81   |

|           | 17.2. Input                                          |       |

|           | 17.3. Output                                         | .81   |

|           | 17.4. Graphical Interface                            | .81   |

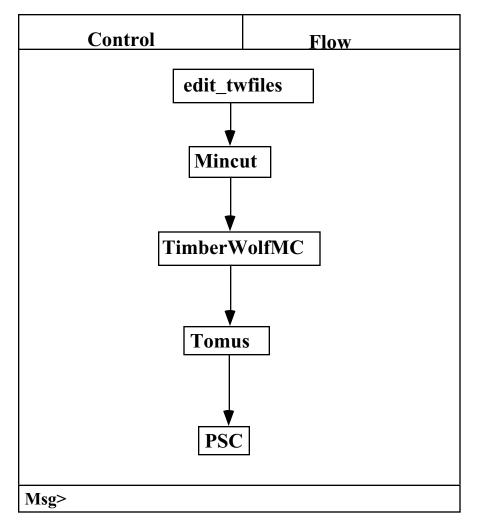

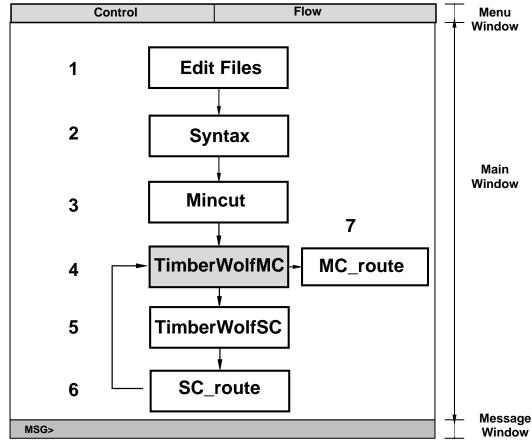

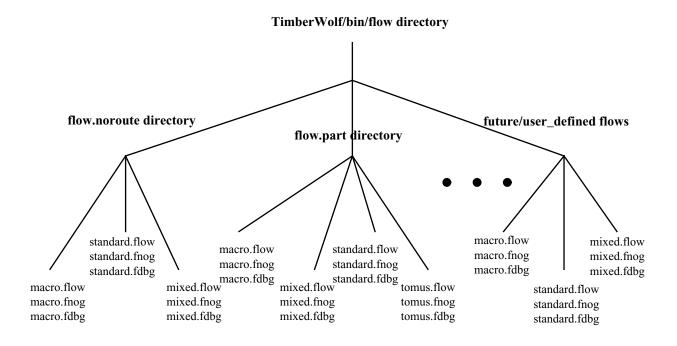

| 18. | TimberWolf (twflow) - The Master Control                  | 82 |

|-----|-----------------------------------------------------------|----|

|     | 18.1. Function                                            |    |

|     | 18.2. Input                                               | 83 |

|     | 18.3. Output                                              | 85 |

|     | 18.4. Graphical Interface                                 |    |

| 19. | TimberWolfMC                                              |    |

|     | 19.1. Function                                            |    |

|     | 19.2. Input                                               |    |

|     | 19.3. Output                                              |    |

|     | 19.4. Graphical Interface                                 |    |

| 20. | TimberWolfSC - Standard cell placement and global routing | 91 |

|     | 20.1. Function                                            | 91 |

|     | 20.2. Input                                               | 91 |

|     | 20.3. Output                                              | 91 |

|     | 20.4. Graphical Interface                                 | 91 |

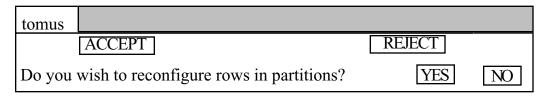

| 21. | Tomus                                                     | 93 |

|     | 21.1. Function                                            | 93 |

|     | 21.2. Input                                               | 93 |

|     | 21.3. Output                                              | 93 |

|     | 21.4. Graphical Interface                                 | 94 |

| 22. | References                                                |    |

| 23. | Appendix A - Syntax for the CircuitName.cel file          | 97 |

|     | 23.1. BNF for circuitName.cel file                        |    |

|     | 23.2. Reserved keywords for circuitName.cel file          |    |

|     | ·                                                         |    |

# TimberWolf-6.1

Mixed Macro / Standard Cell Floorplanning, Placement and Routing Package (Building Block, Gate Array, and Standard Cell Circuits)

#### **1. INTRODUCTION**

TimberWolf [SecS84][SecS85][Sec88b] is a complete timing driven placement and global routing package applicable to row based and building block design styles. TimberWolf is capable of handling any of the row-based design styles, namely, standard cell circuits, gate arrays and sea-of-gates circuits. In addition, TimberWolf is applicable to circuits containing building blocks or macro cells of any rectilinear shape. Furthermore, the cells may have fixed geometry including pin locations (*hard* macro cells) or the cells may have an estimated area with a specified aspect-ratio range, and with pins that need to be placed (*soft* macro cells). TimberWolf is also applicable to floorplanning problems and may be used to completely place and global route mixed macro/standard cell circuits.

### 2. FEATURES

Standard cell, macro cell, and mixed macro/standard cell design styles. Macro cells of any rectilinear shape. Hard and soft macro cells. Gate array designs. X11 (X11R2 - X11R6 inclusive) graphics interface. Based on new simulated annealing algorithm. Signal path-based timing driven. Upper and lower bounds on path lengths. Wire length calculations are based on actual pin locations. Flexible pad placement algorithm. Ability to generate placements close to that obtained from a previous run. Logical pin swapping and/or gate swapping. CPU time control via fast/slow option. Sea-of-gates global router. *N*-way timing driven circuit partitioning. Automatic design flow control.

### 3. Using This Manual

The following conventions are used throughout this guide:

| Boldface         | Boldface letters used in the command or pathname examples indicate keywords |

|------------------|-----------------------------------------------------------------------------|

|                  | that must be used literally.                                                |

| Italic           | Italic letters used in the command or pathname examples indicate user- or   |

|                  | system-supplied data.                                                       |

| <u>Underline</u> | Underlined text indicates default parameter or setting.                     |

| []               | Square brackets enclose optional user-supplied data.                        |

| < >              | Angle brackets enclose specific keyboard key names.                         |

| { }              | Curly brackets enclose a set of user choices.                               |

|                  |                                                                             |

The term *working directory* will refer to the directory of the file system to which the user is currently attached.

3

#### 4. COMPILATION OF TIMBERWOLF

The distribution tape includes all the files necessary to compile TimberWolf version 6.1. TimberWolf is a collection of programs written in C. The programs should port directly to any machine supporting the C language under the UNIX operating system. Supplemental instructions for the compilation are in the file README included in the top level directory. In order to compile and link the program, the UNIX **make** command is utilized. Since it is a rather involved process to compile and link these modules into an executable, it is recommended to use the UNIX makefile which is supplied. We will outline the necessary steps here. First, set the working directory to be the TimberWolf root directory. Next, type **make** in this directory. This should echo the directions we are about to present. The user must first set the TimberWolf directory and **DATADIR** is the pathname of the directory where graphics dumps are stored. **TWDIR** and **DATADIR** can be set to their default settings by typing '**source .twrc** <CR>'. This script will also include the TimberWolf bin directory in the search path.

In order to make the build process as flexible as possible, the makefiles have been split into two pieces, the machine independent part or *Ymakefile* and the machine dependent part or *Ymake.macro* file. To compile on different machines, one only needs to set the compile switches found in the *Ymake.macro* file located in the **./pgms/ymake** directory. For your convenience, various *Ymake.macro* files have been included for frequently used configurations. Either edit the *Ymake.macro* file or copy one of the supplied macro files to *Ymake.macro*.

Several compilation switches in the *Ymake.macro* file require further explanation. The conditional compile switch CLEANUP=-DCLEANUP C should normally be defined when running under the UNIX operating system. If for any reason you do not wish to enable the cleanup handler, you may comment out the CLEANUP definition in the Ymake.macro file. If you wish to install your own cleanup handler instead, see cleanup.h under ./pgms/Ylib/include and cleanup.c under ./pgms/Ylib/lib for more details. If you wish to compile a version of TimberWolf without X11 graphics, the NOGRAPHICS conditional compile is provided. We DO NOT recommend this unless X11 is not supported on your computer. Most workstations support X11, and so the desired method of turning off the graphics is through the use of the **-n** runtime command argument. The macro definitions XLIB and LINKLIB have been furnished to handle cases where the X11 include files and link library have been moved from their standard places: /usr/include/X11 and /usr/lib respectively. The conditional compile SYS5 is useful for compilation on system 5 machines. The DEBUG option normally includes useful debug code into the final executable. If a faster and smaller executable is desired, the *DEBUG* switch may be commented out. Another compilation switch NO\_FEED\_INSTANCES pertains to the feed-through cell naming convention. By default, feed-through cells are given distinct instance names. If you define NO\_FEED\_INSTANCES then each feed will be assigned the same name.

After setting the compilation switches in Ymake.macro, return to the TimberWolf root directory and reset the top level makefile by entering '**ymake**'. We are now ready to reset the makefiles for the rest of the system. This is accomplished by typing '**make Makefiles**' on the command line. At this point, we are ready to build the system by entering '**make install\_non\_yale**'. When the compilation process completes, you will be ready to use TimberWolf.

In designing the TimberWolf system, great pains were made to make the system flexible, portable, and maintainable. Where possible, code is reused through the use of a common library found in ./pgms/Ylib/lib. All graphics calls to X reside in this library. In addition, most system calls are called

5

from library functions. In this way, if any problems arise in the compilation process it will tend to be localized in library routines. All character array sizes can be set with the definition **LRECL** which can be found in **./pgms/Ylib/include/base.h**. In addition, the definitions of int, double, and float may all be redefined in this file to accommodate non-32 bit machine architectures.

**Note**: Never move the TimberWolf tree with a command that does not perserve soft links such as "cp -r". The TimberWolf system will not function if its soft links are destroyed.

#### 5. TIMBERWOLF INPUT FILES

TimberWolf can be executed by issuing the command **TimberWolf** *circuitName*, where *circuitName* is a command line argument specifying the name of the circuit for which the program is to perform placement, global routing, etc. TimberWolf requires the presence of two input files in the working directory: *circuitName.par*, and *circuitName.cel*. The *circuitName.net* file is optional. In addition, the **TWDIR** and **DATADIR** environment variables need to be set to their proper values. Again this can be accomplished by typing 'source .twrc <CR>' in the TimberWolf root directory.

#### 5.1. THE FORMAT OF THE CIRCUITNAME.PAR FILE

The file *circuitName.par* contains parameter specifications for TimberWolf system. The TimberWolf system is a collection of interacting programs. Instead of having parameter files for each of the individual programs, all TimberWolf programs are controlled through the use of a single parameter file. The parameter file consists of two parts: the design rule parameters and program control parameters. Comments are similar to those found in the csh; they are entered by placing a # in the first column of a line. The format for design rule parameters is as follows:

#### RULES

| layer    | layername             | resistance capacitance | { vertical   horizontal } |

|----------|-----------------------|------------------------|---------------------------|

| via      | vianame               | layername              | layername [float]         |

| width    | {layername   vianame} | float                  |                           |

| spacing  | {layername   vianame} | {layername   vianame}  | float                     |

| overhang | {layername   vianame} | {layername   vianame}  | float                     |

| •        |                       |                        |                           |

#### ENDRULES

The mandatory keywords **RULES** and **ENDRULES** delimit the set of design rules. The keyword **layer** defines a layer whose name is given by *layername*. Each layer has associated with it a parasitic resistance and capacitance given in ohms per square and farads per square micron respectively. Concluding the layer definition is the preferred routing direction to be associated with the layer. The preferred direction is used for routing estimation only, the actual routing for a given layer may occur in either direction. At least one layer must be specified in the horizontal direction and at least one must be specified in the vertical direction. Any number of layers may defined. Layer definitions must precede all other rules.

The connections between layers are defined using the keyword **via** followed by the name given to the via cell and the two layers which are to be connected. The via name can then be used in subsequent width and spacing rules. The optional floating point number specifies the aspect ratio limit of the via if rectangular vias are allowed. The detail router will optimize the via dimensions (and orientation) for the given rules while maintaining constant via area. The area is determined from the specified width of the via. The default aspect ratio limit is 1.0.

The keyword **width** allows the definition of a given layer's minimum routing width or via width in microns. Similarly, the **spacing** keyword begins the definition of the minimum distance between any defined layers or vias.

The keyword **overhang** specifies that a layer or via must overlap another layer or via by the amount specified by the floating point number.

The second part of the parameter file is devoted to program control parameters. The format for this file is similar to the .Xdefaults format:

programName\*parameter: parameterValue

where *programName* may be one of the following:

GENR - Genrows - standard cell row configuration program

MICK - Mickey global router

MINC - Mincut clustering program

**PART** - Tomus program (*n*-way partitioner)

SGGR - SGGR (sea-of-gates global router)

TWMC - TimberWolfMC - macro cell placement program

TWSC - TimberWolfSC - row based placement, and global routing program

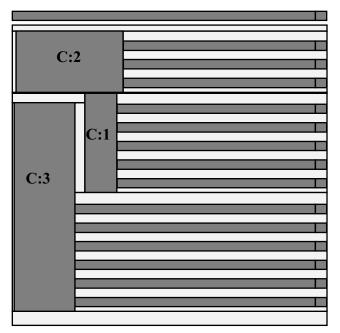

The first time TimberWolf is executed on a design, the TimberWolf system automatically copies a default template for the parameter file from the **./TimberWolf/defaults** directory into the current design directory. The file copied will be **xxx.par** when row-based cells are present and **xxx.macro.par** when only macros are present in the design. Next, the user will be asked to edit the file using vi, or the editor specified in the **EDITOR** cshell environment variable. The user should edit the default values to their appropriate values. Any parameters which are common to all designs should be entered as defaults in the parameter template files. Figure 5.1.1 shows the default xxx.par template file. Note that wildcarding is permitted by preceding the parameter with an asterisk. Each parameter will be discussed in turn below.

#### Sample xxx.par template file

# This is a default parameter file for the TimberWolf system.

# Please change the variables below to their appropriate values.

#

RULES

| layer metal 0.05          | 0.1E-15     | vertical                           |

|---------------------------|-------------|------------------------------------|

| layer poly 20.0           | 0.1E-15     | horizontal                         |

| layer metal2 0.05         | 0.1E-15     | vertical                           |

| via contact metal         | poly        |                                    |

| via via metal             | metal2      |                                    |

| width metal 4.0           |             |                                    |

| spacing metal metal       | 3.0         |                                    |

| width poly 4.0            |             |                                    |

| spacing poly poly         | 3.0         |                                    |

| spacing metal poly        | 0.0         |                                    |

| width contact 2.50        |             |                                    |

| width via 3.0             |             |                                    |

| # this means stacked vias | - a nonzero | number would disallow stacked vias |

| spacing contact via 0     | )           |                                    |

*# this means metal must overlap the contact overhang metal contact 1.0*

#### ENDRULES

# General parameters controlling the TimberWolf system.

\*vertical\_wire\_weight : 1.0

\*vertical\_path\_weight : 1.0

\*rowSep : 1.0

\*padspacing : abut

# Parameters controlling TimberWolfMC. #TWMC\*slow : 2

# Parameters controlling TimberWolfSC. TWSC\*feedThruWidth : 2 layer 1 TWSC\*do.global.route : on

# Parameters controlling genrows configuration program. GENR\*feed\_percentage : 30.0 GENR\*row\_to\_tile\_spacing: 1

Figure 5.1.1

9

| <u>5.</u> 1 | l.1. | <u>Genrows</u> | parameters parameters |

|-------------|------|----------------|-----------------------|

|             |      |                |                       |

| feed_percentage     | float               |

|---------------------|---------------------|

| graphics.wait       | { <u>on</u>   off } |

| minimum_row_len     | integer             |

| numrows             | integer             |

| rowSep              | float               |

| row_to_tile_spacing | integer             |

|                     |                     |

The keyword **feed\_percentage** is followed by a floating point number which specifies the amount of space to be reserved for feedthrough cells. The amount of cell width reserved will be *feed\_percentage* multiplied by the total width of the row-based cells. TimberWolfSC reports the feed percentage of the current execution at the bottom of the circuitName.out file if global routing has been requested.

The **graphics.wait** keyword allows the user to control whether Genrows will enter a wait state after configuring the rows. The default is to wait for the user to enter commands.

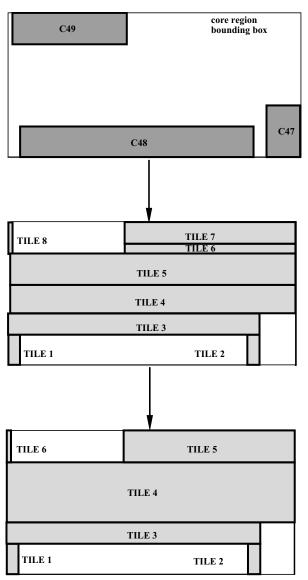

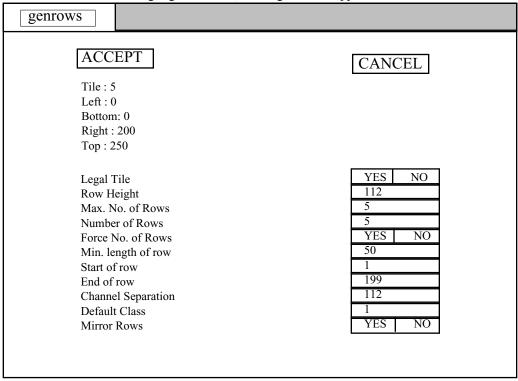

Genrows breaks the core area into tiles. The keyword **minimum\_row\_len** sets a limit on the size of a valid tile, that is, any tile whose width is smaller than the **minimum\_row\_len** will not have rows.

In the case of designs consisting only of row-based cells, the number of cell rows may be set to the value following the keyword **numrows**. This parameter has precedence over the rowSep parameter in calculating the spacing between standard cell rows.

The required keyword **rowSep** is followed by a floating point number representing the desired amount of separation between rows. The amount of separation between rows is this number times the average height of the rows. This is, if you want the row separation equal to the average row height, then this number should be 1.0. On the other hand, if you want the row separation to be twice the height of the rows, then this number should be 2.0. Normally, a value of 1.0 is appropriate.

The optional keyword **row\_to\_tile\_spacing** allows the user to modify the distance between the edge of tile and the beginning and end of a row.

#### 5.1.2. MINC - Mincut parameters max\_macro integer

| mux_muero        | integer |

|------------------|---------|

| numcell_in_macro | integer |

The optional keyword **max\_macro** controls the target number of partitions and the optional keyword **numcell\_in\_macro** controls the maximum number of standard cells to be placed in any standard cell cluster. **WARNING**: these parameters should not be changed from their default values.

#### 5.1.3. MICK - Mickey parameters

There are no user programmable parameters for the Mickey global router at this time.

#### 5.1.4. PART - Tomus parameters

| fast                 | integer |

|----------------------|---------|

| random.seed          | integer |

| rowSep               | float   |

| slow                 | integer |

| vertical_path_weight | float   |

| vertical_wire_weight | float   |

There are no required parameters for controlling the quality of the solution and the CPU time used by Tomus. That is, by default Tomus is set up to yield what we feel approximates the best attainable solutions. However, experienced Tomus users may wish to experiment with the optional parameters for controlling the trade-off between CPU time and solution quality. The keywords **fast** and **slow** represent the set of optional parameters.

The keyword **fast** is an optional entry in the file *circuitName.par*. The inclusion of this keyword will cause Tomus to be executed about n times faster, where n is the value of the integer following the keyword fast. The quality of the placement will tend to decrease as n is made larger than one (the smaller the value of n, the better the result). For design space exploration, a value of n in the range of five to ten is recommended.

The keyword **slow** is an optional entry causing Tomus to be executed about n times longer than the default. The value of n is specified by the integer following the keyword slow. In some cases, you may get a slightly better result. However, only use the slow option if CPU time is of no interest to you.

The keyword **random.seed** is useful when the output data files have been deleted and the data needs to be regenerated. The random number generator seed is printed in the *circuitName.pout* file. If the *circuitName.cel* and *circuitName.par* files are identical, a second run using the same **random.seed** value will yield the exact same output.

The required keyword **rowSep** is followed by a floating point number representing the desired amount of separation between rows. The amount of separation between rows is this number times the average height of the rows. This is, if you want the row separation equal to the average row height, then this number should be 1.0. On the other hand, if you want the row separation to be twice the height of the rows, then this number should be 2.0. Normally, a value of 1.0 is appropriate.

The keyword **vertical\_path\_weight** is required. The floating point number represents the cost for one unit of vertical path length, given that the cost for one unit of horizontal path length is unity. This features allows the user to specify that the capacitance (or, in some sense, the delay) per unit length is different for the vertical routing layer as opposed to the horizontal routing layer. Tomus will seek to ensure that for each path specified in the *circuitName.net* file, the horizontal path length plus vertical\_path\_weight times the vertical path length is above the lower bound and below the upper bound for that path.

### 5.1.5. SGGR - Sea-of-gates global router parameters

| global_routing_iterations | integer             |

|---------------------------|---------------------|

| min_peak_density          | { on   <u>off</u> } |

| min_total_density         | { on   <u>off</u> } |

| TWSC*SGGR                 | { on   <u>off</u> } |

If the TimberWolfSC keyword **SGGR** occurs in the parameter file, the sea-of-gates global router will be executed automatically after the completion of TimberWolfSC if the **do.global.route** keyword is present in the circuitName.par file. SGGR was developed specifically for multiple-metal-layer sea-of-gates circuits and subsequently extended to handle gate arrays and standard cell circuits. If the number of implicit feed through cells (or, implicit feeds) is not enough, SGGR will terminate with a message indicating that this may be the problem. If you get this message, you may restart TimberWolfSC (using the restart mechanism) and request the default global router. You may also leave out the SGGR keyword when you run TimberWolfSC to see how many tracks would be used by the default global router. Then, copy the *circuitName.sav* file to the *circuitName.res* file and rerun TimberWolf, specifying **SGGR**, so that it creates the input files for SGGR. Then, by executing SGGR, you can see how many fewer tracks are needed. In general, the more implicit feeds (or free vertical routing tracks over the rows), the greater the improvement yielded by SGGR over the default global router. Note that **SGGR** is a *TimberWolfSC* keyword.

By default, SGGR seeks to minimize the total channel density for standard cell circuits and seeks to minimize the peak (or maximum) channel density for gate array circuits. The user may override these defaults by specifying the keyword **min\_peak\_density** or the keyword **min\_total\_density** in the .par file. As you would expect, SGGR does a better job of minimizing the maximum channel density (possibly at the expense of higher total channel density) if **min\_peak\_density** is specified, or if the circuit is a gate array and no override is given. Conversely, the total number of tracks will usually be lower (possibly at the expense of a higher peak density) if **min\_total\_density** is specified, or if the circuit is a standard cell circuit and no override is specified.

The keyword **global\_routing\_iterations** followed by an integer modifies the number of global routing iterations that SGGR will perform. The default is three global routing iterations.

#### User data parameters: chip.aspect.ratio float core [initially] integer integer integer default.tracks.per.channel integer gridOffsetX integer gridOffsetY integer gridX integer gridY integer integer minimum\_pad\_space integer integer origin vertical\_path\_weight float vertical\_wire\_weight float Program control: cost\_only on | <u>off</u> } contiguous\_pad\_groups on | off } { do.channel.graph on | <u>off</u> } Ł do.compaction integer do.global.route $\{ on \mid \underline{off} \}$ fast integer graphics.wait $\{ on \mid \underline{off} \}$ no.graphics **on** | <u>**off**</u> } no.graphics.update **on** | <u>**off**</u> } <u>uniform</u> | abut | variable | exact } padspacing print\_pins **on** | <u>off</u> } Ł random.seed integer restart { **on** | <u>**off**</u> } slow integer

#### 5.1.6. TWMC - TimberWolfMC parameters

The keyword **chip.aspect.ratio** is followed by a floating point number which specifies the desired aspect ratio for the chip. TimberWolfMC uses this parameter to compute the dimensions of the core area. The cell placement is influenced in such a manner as to yield an aspect ratio close to the specified value.

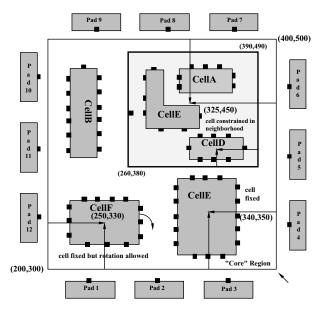

The optional keyword **core** allows the user to specify the exact positions of the chip core area. The four integers following the **core** keyword specifying the dimensions are left side, bottom side, right side, and top side of the chip, respectively. If fixed cells are present in the *circuitName.cel* file, the chip core dimensions should be specified so that a frame of reference is available for determining the fixed cells positions. If the keyword **initially** is specified, TimberWolfMC will determine the core area after

considering the fixed cells; otherwise, TimberWolfMC is constrained to place the cells in the given core area. Unless the user is certain of the routing area of all of the cells, the keyword **initially** *should* be specified.

The optional keyword **default.tracks.per.channel** tells the compaction program and global router to allocate an additional number of tracks (above density) in each channel. The space allocated is the given number of tracks multiplied by the track pitch calculated for that direction value.

Four optional parameters are available for fixing the lower left hand corner of a cell to a grid or lattice, often useful for PCB applications. The parameters **gridX** and **gridY** define the grid to grid spacing in the horizontal and vertical directions, respectively, and the parameters **gridOffsetX** and **gridOffsetY** allow the grid to be shifted from the origin. All four must be specified simultaneously.

The optional keyword **minimum\_pad\_space** allows the user to specify a minimum space between the I/O pads.

The optional keyword **origin** allows the user to specify the origin of the core region. The two integers following the **origin** keyword specify the lower left corner of the core area.

The keyword **vertical\_path\_weight** is required. The floating point number represents the cost for one unit of vertical path length, given that the cost for one unit of horizontal path length is unity. This features allows the user to specify that the capacitance (or, in some sense, the delay) per unit length is different for the vertical routing layer as opposed to the horizontal routing layer. TimberWolfMC will seek to ensure that for each path specified in the *circuitName.net* file, the horizontal path length plus vertical\_path\_weight times the vertical path length is above the lower bound and below the upper bound for that path.

The keyword **cost\_only** is an optional entry in the *circuitName.par* file allowing bypass of the simulated annealing placement algorithm. Its presence will result in TimberWolfMC reading the input file, generating an initial placement from the coordinates given in the input data, computing the initial cost, generating output files, and then terminating.

By default, members of pad groups are placed contiguously. In other words, no nonmember pads can be placed between the member pads. To change the setting to noncontiguous, the parameter value **off** must follow the keyword **contiguous\_pad\_groups**. In this case, nonmember pads could be placed between the pads.

If the optional keyword **do.channel.graph** is present the program will generate a channel graph for a given placement.

The keyword **do.global.route** causes TimberWolfMC to perform a global routing step using the channel graph generated; hence the **do.channel.graph** keyword must be present when requesting global routing.

If **do.compaction** is present in the *circuitName.par* file, the program will iterate the following flow the given number (specified by the integer) of times: compaction, channel generation, global routing. This is the placement modification phase. After each iteration, the space required for routing is accounted for by the compactor, and in the next cycle the program attempts to minimize the chip area using the current knowledge of the routing. Usually three iterations are sufficient for the placement to converge. If compaction is desired, the **do.channel.graph** and **do.global.route** keywords must be present.

By default, TimberWolfMC performs the simulated annealing placement algorithm. The user may control the run time of the simulated annealing algorithm. The keyword **fast** followed by an integer number shortens the running time of the simulated annealing algorithm by the specified integer factor

(possibly at the expense of placement quality). To increase the placement quality (at the expense of running time) use the keyword **slow** followed by an integer multiplying factor. Usually the default amount is sufficient but it is recommended that the **fast** option be used on initial runs. The placement is normally the output of the simulated annealing algorithm; however, the user may specify a placement by fixing all the cells in the *circuitName.cel* file and using the keyword **cost\_only** to avoid TimberWolfMC's placement algorithm.

The graphics system has three control keywords: **no.graphics** which allows the program compiled with the X11 library to run without displaying graphics, **graphics.wait** which tells TimberWolfMC to wait for the user to enter commands after each step in the process, and **no.graphics.update** which does not update the graphics until the end of the simulated annealing run. To continue execution from a graphics wait loop, the user clicks on the FILE menu and selects CONTINUE PGM. See the section on graphics for more details concerning the graphics capabilities and commands.

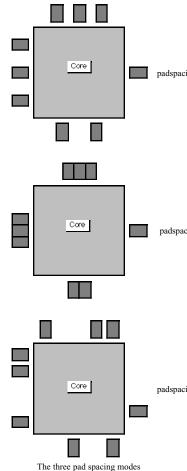

The optional keyword **padspacing** controls the pad spacing mode. The are four modes of operation: **uniform** pad spacing, **abut**ting pad spacing, **variable** pad spacing, padspacing unif**an**d **exact** pad spacing as shown in the illustration.

Uniform pad spacing spaces the pads evenly on each of the sides. In the abut mode, pads are forced to touch one another. The variable pad spacing mode places each pad such that the wirelength is minimized. The last mode turns off the pad spacing algorithm and the pads remain in the place specified by the user in the *circuitName.cel* file. In the first three cases, the side and sidespace constraints padspacing abutare observed. The default mode is uniform padspacing.

The optional keyword **print\_pins** causes TimberWolfMC to output the names of all the one pin nets in the design into the *circuitName.mout* file.

The keyword **random.seed** is useful when the output data files have been deleted and the data needs to be regenerated. The random number generator seed is printed in the *circuitName.mout* file. If the *circuitName.cel*, padspacing variable cuitName.par, and *circuitName.mest* files are identical, a second run using the same **random.seed** value will yield the exact same output. The *circuitName.mest* file should not exist if the run was the first execution of TimberWolfMC.

The optional keyword **restart** must be present in order to resume an execution of TimberWolfMC. This is

useful for resuming a run after a hardware crash or other termination of a run.

5.1.7. TWSC - TimberWolfSC parameters

|          | a parameters:                               |                                              |

|----------|---------------------------------------------|----------------------------------------------|

| User uai | a parameters:<br>approximately_fixed_factor | integer                                      |

|          | feedThruWidth                               | integer layer integer                        |

|          | minimum_pad_space                           | integer layer integer                        |

|          | rowSep                                      | float                                        |

|          | spacer_feed_from_left                       | integer                                      |

|          | spacer_name_twfeed                          | { on   <u>off</u> }                          |

|          | spacer_width                                | integer                                      |

|          | total_row_length                            | integer                                      |

|          | unused_feed_name_twspacer                   |                                              |

|          | vertical_path_weight                        | float                                        |

|          | vertical_track_on_cell_edge                 | { on   <u>off</u> }                          |

|          | vertical_wire_weight                        | float                                        |

| D        |                                             |                                              |

| Program  | n control:                                  |                                              |

|          | absolute_minimum_feeds                      | $\{ on   off \}$                             |

|          | cost_only                                   | $\{ on \mid \underline{off} \}$              |

|          | contiguous_pad_groups                       | $\{ \underline{on} \mid off \}$              |

|          | create_new_cel_file                         | $\{ on \mid \underline{off} \}$              |

|          | do.fast.global.route                        | $\{ on \mid \underline{off} \}$              |

|          | do.global.route                             | { on   <u>off</u> }                          |

|          | fast                                        | integer                                      |

|          | no.graphics                                 | $\{ on \mid \underline{off} \}$              |

|          | graphics.wait                               | { on   <u>off</u> }                          |

|          | no.graphics.update                          | { on   <u>off</u> }                          |

|          | no_explicit_feeds                           | { on   <u>off</u> }                          |

|          | no_feed_at_end                              | { on   <u>off</u> }                          |

|          | old.pin.format                              | { on   <u>off</u> }                          |

|          | orientation_optimization                    | { on   <u>off</u> }                          |

|          | output.at.density                           | { on   <u>off</u> }                          |

|          | padspacing                                  | { <u>uniform</u>   abut   variable   exact } |

|          | pin_layers_given                            | { <u>on</u>   off }                          |

|          | random.seed                                 | integer                                      |

|          | restart                                     | { on   <u>off</u> }                          |

|          | route_only_critical_nets                    | { on   <u>off</u> }                          |

|          | route_padnets_outside                       | { on   <u>off</u> }                          |

|          | SGGR                                        | { on   <u>off</u> }                          |

|          | slow                                        | integer                                      |

|          |                                             |                                              |

The keyword **approximately\_fixed\_factor** modifies the default window for cells which have been approximately fixed. Normally, a cell is constrained to lie within a window centered at the cell's initial position and extending one row above, one row below, and plus or minus one average cell width and three standard deviations in the horizontal direction. The user may globally increase the window size for all approximately fixed cells by entering the keyword **approximately\_fixed\_factor**; the new extent of the window is plus or minus **approximately\_fixed\_factor** rows from the initial position of the cell and plus or minus **approximately\_fixed\_factor** times the default window size in the horizontal direction.

The keyword **feedThruWidth** followed by an integer is required if global routing is desired. The integer informs TimberWolfSC of the width of the feed-through cells that are to be inserted should such be necessary. The **layer** keyword is followed by an integer specifying routing level where this number cross-references the layer definitions found in the RULES section of the parameter file in the order that the layers

were defined. The first layer defined in the RULES section will become layer 1, the second layer will be layer 2, and so forth. If the layer is unknown or does not matter, use layer 0.

The optional keyword **minimum\_pad\_space** allows the user to specify a minimum space between the I/O pads.

The required keyword **rowSep** is followed by a floating point number representing the desired amount of separation between rows. The amount of separation between rows is this number times the average height of the rows. This is, if you want the row separation equal to the average row height, then this number should be 1.0. On the other hand, if you want the row separation to be twice the height of the rows, then this number should be 2.0. Normally, a value of 1.0 is appropriate.

The optional keyword **total\_row\_length** is followed by an integer specifying the total available row length for a gate array circuit (only). That is, this keyword should only be used when the total row length is fixed to a value larger than the total cell width.

For gate arrays, it is often the case that the left edge of a cell must begin on a particular grid. That is, cells need not be adjacent, however, their separation must be a multiple of a certain grid. For example, in the Primary benchmark circuits (1988 International Workshop on Placement and Routing, Research Triangle Park, NC), the placement grid is 20 units. To specify this grid, the user enters the optional keyword **spacer\_width** followed by an integer specifying the grid upon which the left edges of the cells must snap to.

The optional keyword **spacer\_feed\_from\_left** followed by an integer specifies the location of an implicit feed (vertical routing track) relative to the left edge of the spacer, whose width is specified by spacer\_width. For example, on the Primary gate array benchmark circuits, the 20 micron spacer is specified as:

spacer\_width 20

spacer\_feed\_from\_left 0

spacer\_feed\_from\_left 10

spacer\_feed\_from\_left 20

That is, each 20 micron spacer has room for three vertical routing tracks, since the track pitch is 10. In the TimberWolfSC output, the spacer is output as a cell with name GATE\_ARRAY\_SPACER. The leftmost implicit feed has a top pin with name SPACER\_FEED\_TOP\_1 and a bottom pin with name SPACER\_FEED\_BOTTOM\_1. The rightmost (and last) implicit feed pins on the spacer have names SPACER\_FEED\_TOP\_n and SPACER\_FEED\_BOTTOM\_n, where n is the number of implicit feeds on the spacer. Any number of spacer feeds may be specified.

The optional keyword **vertical\_track\_on\_cell\_edge** also pertains to gate arrays. As in the case of the Primary benchmarks, if implicit feeds are present on both the left and right edges of each cell, then on any two adjacent cells, two feeds (one from each cell) will overlap. The keyword **vertical\_track\_on\_cell\_edge** will eliminate the possibility of overlapping feeds due to the specification of implicit feeds on both the left and right edges of the cells.

The keyword **spacer\_name\_twfeed** is an optional, and is only applicable if the user has selected the gate array mode. As presented earlier, the default name of the spacer cell is GATE\_ARRAY\_SPACER. If the **spacer\_name\_twfeed** keyword is entered in the *circuitName.par* file, then the name of the spacer cell will be twfeed instead. Note that the names of the pins on the spacer cell will be the same.

Although the TimberWolfSC global routing algorithm is such that few unused feed through cells are placed into the rows, the user may want to remove all unused feed through cells. It is unwise to simply remove these from the .pl1 file since that would invalidate the global routing (as stored in the .pin file). In an attempt to aid the user in identifying which feeds in the .pl1 file are unused, the selection of the **unused\_feed\_name\_twspacer** keyword changes the name of each unused feed from its usual name twfeed (concatenated with a unique integer) to twspacer (concatenated with a unique integer).

The keyword **vertical\_path\_weight** is required. The floating point number represents the cost for one unit of vertical path length, given that the cost for one unit of horizontal path length is unity. This features allows the user to specify that the capacitance (or, in some sense, the delay) per unit length is different for the vertical routing layer as opposed to the horizontal routing layer. TimberWolfSC will seek to ensure that for each path specified in the *circuitName.net* file, the horizontal path length plus vertical\_path\_weight times the vertical path length is above the lower bound and below the upper bound for that path.

Inclusion of the **absolute\_minimum\_feeds** keyword implies that the global router is to insert an absolute minimum of explicit feedthrough cells. This minimum is dictated by the placement. This keyword should not be chosen routinely since it may cause the global router to use additional routing tracks. However, for gate arrays in which explicit feeds cannot be added, this keyword can be used to advantage. For example, if the global router added a few feeds, then execute a second run using this keyword. In general, significantly fewer feeds will be used, although accompanied (usually) with an increase in routing tracks.

The keyword **cost\_only** is an optional entry in the file *circuitName.par*. Its presence will result in TimberWolfSC reading the input files, generating an initial placement, computing the initial cost, generating the output files, and then graceful death. Including this keyword is highly recommended on the first run on the input files. Any errors will be directed to the output file called *circuitName.out*.

By default, members of pad groups are placed contiguously. In other words, no nonmember pads can be placed between the member pads. To change the setting to noncontiguous, the parameter value **off** must follow the keyword **contiguous\_pad\_groups**. In this case, nonmember pads could be placed between the pads.

The optional keyword **create\_new\_cel\_file** instructs TimberWolfSC to create a new *circuitName.ncel* at the end of the run which contains the final placement information by using the initially keyword. The choice of **fixed**, **nonfixed**, **approximately\_fixed**, or **rigidly\_fixed** is based on the selection in the original circuitName.cel. For example, if a cell was originally specified with the fixed keyword, then that keyword will be used in the new *circuitName.ncel* file. If no initial placement was specified for a given cell, then the keyword **nonfixed** will be used in the new .ncel file. A new *circuitName.ncel* file will overwrite any existing *circuitName.ncel file*. Move it to *circuitName.cel* and rerun TimberWolf.

There are no required parameters for controlling the quality of the solution and the CPU time used by TimberWolfSC. That is, by default TimberWolfSC is set up to yield what we feel approximates the best attainable solutions. However, experienced TimberWolfSC users may wish to experiment with the optional parameters for controlling the trade-off between CPU time and solution quality. The keywords fast and slow represent the set of optional parameters.

The keyword **fast** is an optional entry in the file *circuitName.par*. The inclusion of this keyword will cause TimberWolfSC to be executed about *n* times faster, where *n* is the value of the integer following the

keyword **fast**. The quality of the placement will tend to decrease as n is made larger than one (the smaller the value of n, the better the result). However, it is our experience that TimberWolfSC will outperform other placement algorithms even with n set in such a manner that the run time of TimberWolfSC matches the run time of the other (faster) algorithm. For chip-planning applications, a value of n in the range of five to ten is recommended.

The keyword **slow** is an optional entry causing TimberWolfSC to be executed about n times longer than the default. The value of n is specified by the integer following the keyword slow. In some cases, you may get a slightly better result. However, only use the slow option if CPU time is of no interest to you.

The presence of the optional keyword **do.global.route** will result in TimberWolfSC completing a global routing step. Following this step, pins have been selected for interconnection in particular channels so as to minimize the total number of wiring tracks required. TimberWolfSC optimizes net segment placement (which side of a row to place a net segment, when it is switchable) so as to reduce the number of wiring tracks required. In this step, the pins for each net are assigned a group number. Pins with the same group number are to be connected. More details are available in Section 6 on the presentation of the *circuitName.pin* file.

Currently, there are two global routers: an internal global router useful for standard cell and gate array circuits which can add additional feedthroughs to complete the routing, and SGGR, a sea-of-gates global router developed specifically for multiple-metal-layer sea-of-gates circuits and subsequently extended to handle gate arrays and standard cell circuits. If the number of implicit feed through cells (or, implicit feeds) is not enough, SGGR will terminate with a message indicating that this may be the problem. If you get this message, you may restart TimberWolfSC (using the restart mechanism) and request the default global router. If the keyword **SGGR** is specified, SGGR will be executed; otherwise, the default global router will be run. In both cases, the keyword **do.global.route** must be turned on.

The graphics system has three control keywords: **no.graphics** which allows the program compiled with the X11 library to run without displaying graphics, **graphics.wait** which tells TimberWolfSC to wait for the user to enter commands after each step in the process, and **no.graphics.update** which does not update the graphics until the end of the simulated annealing run. To continue execution from a graphics wait loop, the user clicks on the FILE menu and selects CONTINUE PGM. See the section on graphics for more details concerning the graphics capabilities and commands.

The new pin output format outputs a pseudopin for every connection to a macro or pad whereas the old format only outputs a pseudopin only for nets that leave the channel. If the old format is desired, use **old.pin.format** (not recommended).

The optional keyword **orientation\_optimization** instructs TimberWolfSC to perform only the following steps: read the initial placement information from the *circuitName.cel* file, optimize the orientation of the cells, and execute the global router.

If the keyword **output.at.density** is present, the placement will be output according to the density determined by the global router. This should *not* be used in the case of mixed macro/standard cell circuits.

The optional keyword **padspacing** controls the pad spacing mode. The are four modes of operation: **uniform** pad spacing, **abut**ting pad spacing, **variable** pad spacing, and **exact** pad spacing. Uniform pad spacing spaces the pads evenly on each of the sides. In the abut mode, pads are forced to touch one another. The variable pad spacing mode places each pad such that the wirelength is minimized. The last mode turns off the pad spacing algorithm and the pads remain in the place specified by the user in the *circuitName.cel*  file. In the first three cases, the side and sidespace constraints are observed. The default mode is uniform padspacing.

Normally, the pin layers must be specified. If the keyword **pin\_layers\_given** is assigned the parameter value **off**, the pin's layer does not need to be defined, and thus, backward compatibility with older versions of TimberWolfSC is maintained. Warning: this is only true when TimberWolfSC is run as a stand alone program.

The keyword **random.seed** is useful when the output data files have been deleted and the data needs to be regenerated. The random number generator seed is printed in the *circuitName.out* file. If the *circuitName.cel* and *circuitName.par* files are identical, a second run using the same **random.seed** value will yield the exact same output.

The optional keyword **restart** must be present in order to resume an execution of TimberWolfSC. This is useful for resuming a run after a hardware crash or other termination of a run. Crash recovery will be discussed later.

Normally, the TimberWolfSC internal global router has the freedom to insert feedthroughs to connect pins in the interior of the core area to pins on the I/O pads at the perimeter of the design if the wirelength or congestion is minimized. If the keyword **route\_padnets\_outside** is present, the routing will instead be forced to leave the channel in which the interior pins reside, and enter the channels which surround the core region. This will minimize feedthroughs but may lengthen the wirelength and increase the congestion outside the core area.

#### 5.2. THE FORMAT OF THE CIRCUITNAME.CEL FILE

The file *circuitName.cel* contains the descriptions of the standard cells (row-based cells), macro cells and pads, as well as the netlist. Comments may be added using C-style comments ( /\* \*/ ) with the restriction that comments are no longer than 2000 characters in length. The description *must* be ordered as follows: standard cells must precede the macro cells which must precede the pads. The complete BNF for the TimberWolf system is given in Appendix A. Each entry in *circuitName.cel* for row-based cells takes on the following form:

#### 5.2.1. Standard Cell / Gate Array Cell Definition

```

cell string string

[legal_block_classes n block_class_1 .... block_class_n]

[swap_group string ]

[ ECO_added_cell ]

[ nomirror ]

[ initially { fixed | nonfixed | approximately_fixed | rigidly_fixed } integer from {left |

right} of block integer ]

[ orient { 0 | 1 | 2 | 3 } ]

left integer right integer bottom integer top integer

pin name string signal string layer integer integer integer

[equiv name string layer integer integer ]

pin name string signal string layer integer integer integer

[unequiv name string layer integer integer ]

[ pin_group

pin name string/string signal string layer integer integer integer

[equiv name string/string layer integer integer ]

pin name string/string signal string layer integer integer integer

[equiv name string/string laver integer integer ]

end_pin_group ]

```

The keyword **cell** begins the description of a cell. The string following the keyword **cell** is ignored completely by TimberWolf. It can be used for any purpose by the user. The second string following the keyword cell must be the *name* of the cell. TimberWolf outputs the placement information in terms of these cell names.

The next line in the description of a cell is optional. The **legal\_block\_classes** feature allows the user to constrain each cell to a set of block classes. Here, *n* is an integer specifying how many block classes you are going to list, followed by a list of integers -- each one of which is a block class as defined in the Genrows program. The block class definitions are generated by the Genrows program and output into the *circuitName.blk* file. Genrows will allow the user to associate a class number with any of the rows as shown below in the examples. The blocks listed in the *circuitName.blk* file are listed from the top but numbered from the bottom on the screen

```

cell 18 latch

legal_block_classes 3 8 5 9

left ...

```

This implies that the cell named *latch* must be confined to the rows whose block class is one of 8, 5 or 9. Keep in mind that any number of rows may have been specified as having a given block class.

If a cell is to be allowed in any row, then simply don't include a legal\_block\_classes line.

EXAMPLE 2:

.blk file:

| row 6 |     |     |     |         |             |

|-------|-----|-----|-----|---------|-------------|

| row 0 | 11  | 123 | 37  | class 1 | (first row) |

| row 0 | 63  | 123 | 89  | class 1 |             |

| row 0 | 115 | 123 | 141 | class 2 |             |

| row 0 | 187 | 123 | 193 | class 2 |             |

| row 0 | 219 | 123 | 245 | class 3 |             |

| row 0 | 271 | 123 | 297 | class 3 | (last row)  |

Suppose that the description of a cell includes the following line in the .cel file:

```

legal_block_classes 2 1 2

```

This specifies that the cell is confined to rows 1 through 4. Further, suppose that the description of a cell includes the following line:

```

legal_block_classes 2 1 3

```

This specifies that the cell is confined to rows 1 or 2, or, 5 or 6. Note that a cell in the .cel file without a **legal\_block\_classes** line can go into any of rows 1 through 6. Alternatively, you could also specify a line as follows if that was what you wanted:

legal\_block\_classes 3 1 2 3

Another new optional feature is the gate swapping facility. Any cells which are to participate in gate swapping must have a line as follows:

#### swap\_group string

If you want gate swapping to occur between two or more cells, then you must give each of the particular cells the same **swap\_group**. The gate swapping facility is accomplished by exchanging groups of pins between any cells which have the same swap\_group. See the section on pin groups for more details on defining the groups of pins to be swapped.

Another optional feature is the Engineering Change Order (ECO) handling capability. This feature is useful when additional standard cells have been added to the netlist, and yet you want the placement of the "old" cells to remain essentially exactly in their positions as determined by a previous run. The "old" placement information must be given in the .cel by means of the **initially** keyword (any of fixed,

nonfixed, etc. may be used since when ECO requests are present in the *circuitName.cel* file, the placement of the "old" cells will be unchanged relative to their initial specification). Any cell having the following line within its description

#### ECO\_added\_cell

will have its initial placement information completely disregarded. Instead, a quick procedure which is a variant of force-directed placement is used to place the new cell to minimize total wire length.

If you anticipate making use of this ECO capability, then it would be very useful to *always* place the keyword **create\_new\_cel\_file** in the *circuitName.par* file. Then, if you find that cells are to be added (or deleted), simply add (or delete) these cells from the previously generated *circuitName.ncel* file. Be sure to append the line

#### ECO\_added\_cell

to the description of the added cells and then make this new *circuitName.ncel* file to be the new *circuitName.cel* file. The execution of TimberWolf will then quickly yield an updated placement, preserving the locations of the "old" cells and placing the new cells while seeking to minimize the total wire length.

This feature is particularly useful for generating a subsequent placement which is close to that obtained from a previous run. For example, suppose a great deal of effort was made to get a particular placement correct with respect to timing restrictions. However, suppose that the designer then adds or deletes cells or nets from the .cel file, or changes the number of rows. A new TimberWolf run will generate a completely different placement, one that probably has a similar total wire length and chip area, but one with a whole new set of timing problems, etc. Hence, for such a subsequent placement, one would very much like to preserve the general character of the previous placement. This can now be achieved.

The keyword **nomirror** is optional and specifies that a cell in a row cannot have its *x*-coordinates mirrored. By default, mirroring is allowed. This should come before the preplacement option.

Preplacing a cell is optional. This is accomplished with the keyword **initially** followed by one of four choices for the subsequent keyword: fixed, nonfixed, approximately\_fixed, and rigidly\_fixed. If fixed is specified, the cell is to remain fixed at the specified location, whereas, **nonfixed** allows the cells to move from their specified initial positions. The integer following **fixed** or **nonfixed** represents how far from the left or right end of a row the cell should be placed initially. Following the keyword from, the user selects either left or right to indicate whether the integer represents a distance from the left or right end of the row. If the user selects left, then the distance is the amount the left edge of the cell is to be placed from the left end of the block (row). On the other hand, if the user selects **right**, then the distance is the amount the right edge of the cell is to be placed from the right end of the block. Following the keywords of and block is an integer specifying the block (row) into which the cell is to be placed initially. This integer represents a row number, in which the rows are numbered starting from the bottom of the layout. The approximately fixed keyword instructs TimberWolf to keep the placement of this cell *close* to its initial position. The cell is constrained to lie within a window centered at the cell's initial position and extending one row above, one row below, and plus or minus one average cell width and three standard deviations in the horizontal direction. The user may globally increase the window size for all approximately fixed cells by entering the keyword approximately\_fixed\_factor in the .par file:

TWSC\*approximately\_fixed\_factor: integer

If this keyword is found in the .par file, the extent of the window is plus or minus

**approximately\_fixed\_factor** rows from the initial position of the cell and plus or minus **approximately\_fixed\_factor** times the default window size in the horizontal direction. Gate array mode is triggered by the presence of **rigidly\_fixed** cells, which in turn requires the presence of the spacer\_width keyword. The use of the **rigidly\_fixed** keyword means that the cell *must* end up at *exactly* that coordinate.

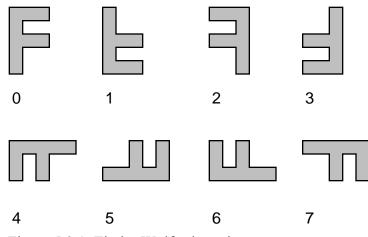

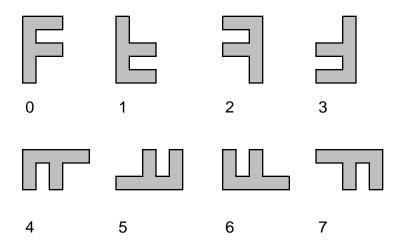

The user may input an initial cell orientation for row-based cells through the use of the keyword **orient** followed by an integer. Note that the value of the integer must be one of 0, 1, 2, or 3. The meaning of the orientation numbers is presented in section 5.2.2.

The line beginning with the keyword **left** is required. Each keyword **left**, **right**, **bottom**, and **top** is followed by an integer representing the distance of each edge from the exact center of the cell. If a cell has an odd width, the *x*-center is truncated to form an integer. Note that the integers following **left** and **bottom** are necessarily negative and that the integers following **right** and **top** are necessarily positive. Furthermore, the following relationships must hold:

right - | left |= 0 or 1right + left= 0 or 1top - | bottom |= 0 or 1top - bottom= 0 or 1

The remainder of the description of a cell indicates the position of the pins and the signal or net names associated with each pin.

Each pin description begins with the keyword **pin** and is followed by the keyword **name** which is in turn followed by a string representing the name of the pin. Following the keyword **signal** is a string representing the name of the signal or net to which this pin is to be connected.

The **layer** keyword is followed by an integer specifying routing level. This number cross-references the layer definitions found in the RULES section of the parameter file in the order that the layers were defined. The first layer defined in the RULES section will become layer 1, the second layer will be layer 2, and so forth. If the layer is unknown or does not matter, use layer 0.

The pair of integers following the layer definition represent the *x*-*y* coordinates of the location of the pin *relative* to the center of the cell. Pins do not have to be on the boundary but they may not be outside the boundary.

The description of an equivalent (or internally connected) pin begins with the keyword **equiv** and is followed by the keyword **name** which in turn is followed by a string representing the name of this pin. Next, the layer information is specified using the layer keyword followed by the routing level. Following the layer definition are two integers specifying the location of the equivalent pin relative to the center of the cell. Note that pins described by **equiv** are assumed to be connected to the same signal or net name as the last entered pin whose description begins with the keyword **pin**.

If only one of an electrically-equivalent pair of pins can be used (for example, because the resistance of the poly line connecting them is too high), the description of the equivalent pin must begin with the keyword **unequiv**. The keyword **unequiv** is followed by the keyword **name** which in turn is followed by a string representing the name of the unequivalent pin. Next are two integers specifying the location of the unequivalent pin relative to the center of the cell. Note that pins described by **unequiv** are assumed to be connected to the same signal or net name as the last entered pin whose description begins with the keyword

**pin.** Following a pin description beginning with **pin**, any number of pin descriptions beginning with **equiv** may follow. However, only one **unequiv** may be specified following a pin description beginning with the keyword **pin**.

An example of a cell description in which the cell is to be preplaced and mirroring is not allowed is shown below.

cell 78 ABcell8 nomirror initially fixed 0 from left of block 3 left -50 right 50 bottom -25 top 25 pin name pin2 signal A layer 1 0 25 equiv name pin2 layer 1 0 -25

This is an example of the description of a nonpreplaced cell in which mirroring is allowed.

cell 79 ABcell11 left -50 right 50 bottom -25 top 25 pin name pin5 signal C layer 0 0 25 equiv name pin5 layer 0 0 -25

TimberWolf supports implicit feed throughs (or built-into-the-cell feeds), common in multiple metal circuits. The user must enter the signal name **TW\_PASS\_THRU** for any such pins. If implicit feed-through paths are present, TimberWolf will use such a path instead of inserting a feed-through cell whenever possible. An example follows:

*cell* 1 cell1 *left* -50 *right* 50 *bottom* -25 *top* 25 *pin name* 1 *signal* TW\_PASS\_THRU layer 2 30 -52 *equiv name* 2 *layer* 2 30 53 *pin name* 3 *signal* TW\_PASS\_THRU layer 2 -30 -52 *equiv name* 4 *layer* 2 -30 53

The optional keyword **pin\_group** begins the definition of a swappable gate. The set of pins on a cell which constitute a gate are delineated as follows:

```

pin_group

pin name 1/a signal S14 layer 2 -9 -24

equiv name 1/a layer 2 -9 24

pin name 2/a signal S13 layer 2 -15 -24

equiv name 2/a layer 2 -15 24

pin name 3/a signal S12 layer 2 -11 -24

equiv name 3/a layer 2 -11 24

end_pin_group

```

Note that the keyword **pin\_group** functions as a "begin" in PASCAL or a "{" in C. Similarly, **end\_pin\_group** functions as an "end" or "}". Obviously it is assumed that each pin group within a swap\_group has the same number of pins. Note that the "/" is a *required* part of the pin name for each pin in a *gate*. When swapping two gates, the pins are swapped on a one-to-one basis. It must be the case that for any pin within a gate, there is a corresponding pin in the other gate such that the pin names prior to the

23

"/" match. The portion of the pin name after the "/" is used to ensure uniqueness for the complete pin name.

Note further that by defining each "gate" to consist of a single pin and by giving each cell a unique **swap\_group**, then TimberWolf will in effect optimize the layout taking into account the logical equivalence of pins within each cell.

Finally, keep in mind that the pin names stay local to their original cells in the output files.

#### EXAMPLE:

(two cells belonging to the same swap group where each has one swappable gate)

cell 337 U3 swap\_group U3-U4 left -16 right 16 bottom -24 top 24 pin name 00#I01 signal S1088 layer 1 11 -24 equiv name 01#I01 layer 1 11 24 pin name 00#I02 signal S1090 layer 1 13 -24 equiv name 01#I02 layer 1 13 24 pin\_group pin name 5/a signal S14 layer 1 -9-24 equiv name 5/a layer 1 -9 24 pin name 6/a signal S13 layer 1 -15 -24 equiv name 6/a layer 1 -15 24 pin name 7/a signal S12 layer 1 -11-24 equiv name 7/a layer 1 -11 24 end\_pin\_group pin name 00#TW\_1 signal TW\_PASS\_THRU layer 1 -13 -24 equiv name 01#TW\_1 layer 1 -13 24 pin name 00#TW\_2 signal TW\_PASS\_THRU layer 1 -7 -24 equiv name 01#TW\_2 layer 1 -7 24 pin name 00#TW\_3 signal TW\_PASS\_THRU layer 1 -5 -24 equiv name 01#TW\_3 layer 1 -5 24 pin name 00#TW\_4 signal TW\_PASS\_THRU layer 1 -3 -24 equiv name 01#TW\_4 layer 1 -3 24 pin name 00#TW\_5 signal TW\_PASS\_THRU layer 1 -1 -24 equiv name 01#TW 5 layer 1 -1 24 pin name 00#TW\_6 signal TW\_PASS\_THRU layer 1 1 -24 equiv name 01#TW\_6 layer 1 1 24 pin name 00#TW\_7 signal TW\_PASS\_THRU layer 1 3 -24 equiv name 01#TW\_7 layer 1 3 24

cell 448 U4 swap\_group U3-U4 left -16 right 16 bottom -24 top 24 pin name 00#I01 signal S1088 layer 1 11 -24 equiv name 01#I01 layer 1 11 24 pin name 00#I02 signal S1089 layer 1 13 -24 equiv name 01#I02 layer 1 13 24 pin\_group pin name 5/b signal S19 layer 1 -9-24 equiv name 5/b layer 1 -9 24 pin name 6/b signal S18 layer 1 -15 -24 equiv name 6/b layer 1 -15 24 pin name 7/b signal S17 layer 1 -11 -24 equiv name 7/b layer 1 -11 24 end\_pin\_group pin name 00#TW\_1 signal TW\_PASS\_THRU layer 1 -13 -24 equiv name 01#TW\_1 layer 1 -13 24 pin name 00#TW\_2 signal TW\_PASS\_THRU layer 1 -7 -24 equiv name 01#TW\_2 layer 1 -7 24 pin name 00#TW\_3 signal TW\_PASS\_THRU layer 1 -5 -24 equiv name 01#TW\_3 layer 1 -5 24 pin name 00#TW\_4 signal TW\_PASS\_THRU layer 1 -3 -24 equiv name 01#TW\_4 layer 1 -3 24 pin name 00#TW\_5 signal TW\_PASS\_THRU layer 1 -1 -24 equiv name 01#TW\_5 layer 1 -1 24 pin name 00#TW\_6 signal TW\_PASS\_THRU layer 1 1-24 equiv name 01#TW\_6 layer 1 1 24 pin name 00#TW 7 signal TW PASS THRU layer 1 3-24 equiv name 01#TW\_7 layer 1 3 24

*Unused gates* in a cell can also be defined. That is, the pins comprising such a gate are available to be used as pass throughs during global routing. **TW\_SWAP\_PASS\_THRU** is the signal name for pass throughs on gates (recall that **TW\_PASS\_THRU** is the proper signal name for regular pass throughs on a cell).

In the example below, note that their are six gates defined among the three cells. Three of the six gates are *unused*. At the end of a TimberWolf run, any of the six gates could end up on any of the three cells.

25

#### EXAMPLE:

cell 554 U5 swap\_group U5-U6-U7 left -16 right 16 bottom -24 top 24 pin name 00#101 signal S1088 layer 1 11 -24 equiv name 01#I01 layer 1 11 24 pin name 00#102 signal S1093 layer 1 13 -24 equiv name 01#I02 layer 1 13 24 pin name 00#I04 signal S22 layer 1 -9 -24 equiv name 01#I04 layer 1 -9 24 pin\_group pin name 1/a signal S21 layer 1 -15 -24 equiv name 1/a layer 1 -15 24 pin name 2/a signal S20 layer 1 -11 -24 equiv name 2/a layer 1-11 24 end\_pin\_group pin\_group pin name 1/b signal TW\_SWAP\_PASS\_THRU layer 1 -13 -24 equiv name 1/b layer 1 -13 24 pin name 2/b signal TW\_SWAP\_PASS\_THRU layer 1 -7 -24 equiv name 2/b layer 1 -7 24 end\_pin\_group pin name 00#TW\_3 signal TW\_PASS\_THRU layer 1 -5 -24 equiv name 01#TW\_3 layer 1 -5 24 pin name 00#TW\_4 signal TW\_PASS\_THRU layer 1 -3 -24 equiv name 01#TW\_4 layer 1 -3 24 pin name 00#TW\_5 signal TW\_PASS\_THRU layer 1 -1 -24 equiv name  $01\#TW_5$  layer 1 -1 24 pin name 00#TW\_6 signal TW\_PASS\_THRU layer 1 1-24 equiv name 01#TW\_6 layer 1 1 24 pin name 00#TW\_7 signal TW\_PASS\_THRU layer 1 3 -24 equiv name 01#TW\_7 layer 1 3 24

27

cell 655 U6 swap\_group U5-U6-U7 left -16 right 16 bottom -24 top 24 pin name 00#I01 signal S1088 layer 1 11 -24 equiv name 01#I01 layer 1 11 24 pin name 00#I02 signal S1097 layer 1 13 -24 equiv name 01#I02 layer 1 13 24 pin name 00#I04 signal S25 layer 1 -9 -24 equiv name 01#I04 layer 1 -9 24 pin\_group pin name 1/c signal S24 layer 1 -15 -24 equiv name 1/c layer 1 -15 24 pin name 2/c signal S23 layer 1 -11 -24 equiv name 2/c layer 1 -11 24 end\_pin\_group pin\_group pin name 1/d signal TW\_SWAP\_PASS\_THRU layer 1 -13 -24 equiv name 1/d layer 1 -13 24 pin name 2/d signal TW\_SWAP\_PASS\_THRU layer 1 -7 -24 equiv name 2/d layer 1 -7 24 end\_pin\_group pin name 00#TW\_3 signal TW\_PASS\_THRU layer 1 -5 -24 equiv name 01#TW\_3 layer 1 -5 24 pin name 00#TW\_4 signal TW\_PASS\_THRU layer 1 -3 -24 equiv name 01#TW\_4 layer 1 -3 24 pin name 00#TW\_5 signal TW\_PASS\_THRU layer 1 -1 -24 equiv name 01#TW\_5 layer 1 -1 24 pin name 00#TW\_6 signal TW\_PASS\_THRU layer 1 1 -24 equiv name 01#TW\_6 layer 1 1 24 pin name 00#TW\_7 signal TW\_PASS\_THRU layer 1 3 -24 equiv name 01#TW\_7 layer 1 3 24

cell 745 U7 swap\_group U5-U6-U7 left -16 right 16 bottom -24 top 24 pin name 00#I01 signal S1088 layer 1 11 -24 equiv name 01#I01 layer 1 11 24 pin name 00#I02 signal S16 layer 1 13 -24 equiv name 01#I02 layer 1 13 24 pin name 00#I04 signal S28 layer 1 -9 -24 equiv name 01#I04 layer 1 -9 24 pin\_group pin name 1/e signal S27 layer 1 -15 -24 equiv name 1/e layer 1 -15 24 pin name 2/e signal S26 layer 1 -11 -24 equiv name 2/e layer 1 -11 24 end\_pin\_group pin\_group pin name 1/f signal TW\_SWAP\_PASS\_THRU layer 1 -13 -24 equiv name 1/f layer 1 -13 24 pin name 2/f signal TW\_SWAP\_PASS\_THRU layer 1 -7 -24 equiv name 2/f layer 1 -7 24 end\_pin\_group pin name 00#TW\_3 signal TW\_PASS\_THRU layer 1 -5 -24 equiv name  $01\#TW_3$  layer 1 -5 24 pin name 00#TW\_4 signal TW\_PASS\_THRU layer 1 -3 -24 equiv name 01#TW\_4 layer 1 -3 24 pin name 00#TW\_5 signal TW\_PASS\_THRU layer 1 -1 -24 equiv name 01#TW\_5 layer 1 -1 24 pin name 00#TW\_6 signal TW\_PASS\_THRU layer 1 1 -24 equiv name 01#TW\_6 layer 1 1 24 pin name 00#TW\_7 signal TW\_PASS\_THRU layer 1 3 -24 equiv name 01#TW\_7 layer 1 3 24

#### 5.2.2. Hard Macro Cell Definition

We will now describe the arbitrary rectilinear shaped cells known as macros. Hard macro cells are cells in which all geometric information is known. They are described as follows:

```

hardcell string name string

[fixed at integer from { L | R } integer from { B | T } ]

[ fixed neighborhood

integer from { L | R } integer from { B | T }