A Field-Programmable Analog Array

Our FPAA development is a joint effort of APL (Tim Edwards, designer; Kim Strohbehn, design support; Mark Martin, design support; Steve Jaskulek, principal investigator) and Actel Corporation (John McCollum, principal contact; Dan Wang and Chin Li, technical support). The project is one of the premier initiatives of the Advanced Technology Development program (ATD), sponsored by NASA and JPL.

The FPAA we are developing assumes that a substantial market for FPAA devices exists in the Space community (manufacturers of satellites and deep space probes). Unlike analog circuit design on terra firma, conditions in space necessitate making all circuits tolerant to large doses of radiation (just how large depends on the location of the spacecraft and the duration of its mission). Actel corporation has targeted the Space technology niche for radiation-tolerant FPGAs, and produces chips regularly on several special fabrication processes specializing in radiation hardness. The use of chips which are pre-qualified for spaceflight results in a substantial reduction in development time of spacecraft electronics. However, no equivalent path currently exists for analog circuit development. All analog circuits on board spacecraft, from the delicate sensor preamplifers down to the lowly housekeepking circuits, must go through the lengthy process of flight qualification, which can become extremely expensive and time consuming if errors in the circuit design are found and changes required.

The FPAA we are developing is a one-time programmable array of standard analog components (amplifier, resistors, capacitors, and analog switches) fabricated using Actel's metal-to-metal antifuse technology on the latest RT-SX radiation-tolerant fabrication process. Our goal is to meet the needs of space technology manufacturers for fast-turnaround-time and low-cost development of analog circuits for spaceflight applications.

The first paper to appear on this project was presented at the MAPLD 1999 Conference (Military and Aerospace Applications of Programmable Devices and Technology. . . the name has escaped the bounds of its own acronym) at the JHU Applied Physics Laboratory, September 28-30, 1999.

Both the paper (PostScript and HTML) and the presentations (overhead transparencies, also in PostScript) are available below.

Preliminary testing results from July 2000 indicate that the FPAA chip is completely functional. Further tests will determine the performance of the analog parts, after the prototype programmer is replaced with a clean circuit board test setup.

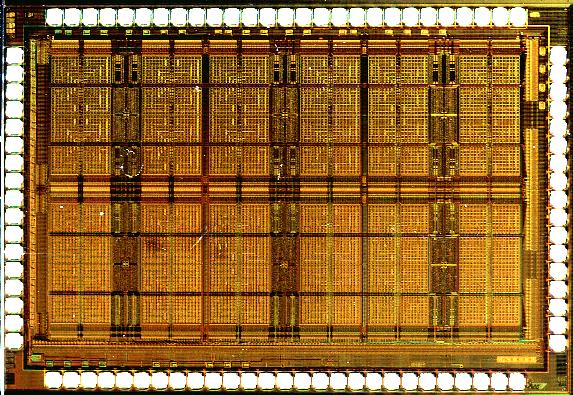

Below is a photograph of the FPAA die.

Our next goal, pending continued funding, is to extend the FPAA to a true mixed-signal array (FPMA) by adding a substantial number of programmable digital modules to the design. Also, we will expand the analog architecture and attempt to squeeze more analog performance out of the digital fabrication process.

![]()

email: tim@stravinsky.jhuapl.edu

Last updated: July 23, 2014 at 9:18pm